Faqs: Wie lange ist der Vermittlungscode gültig? Gibt es ... - zeitl. länge

Once we have extended the uvm_sequencer class, we can add the desired additional features to our custom sequencer. These features may include customized data handling, specialized transaction generation, or any other functionality required for the testbench. By tailoring the sequencer to our specific needs, we enhance its capability to drive the desired stimulus and perform targeted testing.

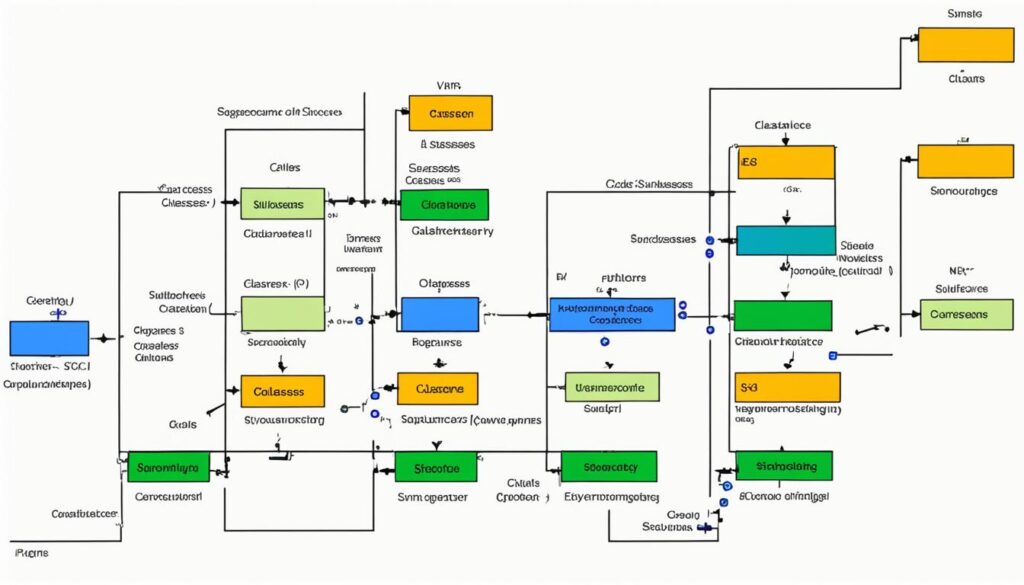

The uvm_sequencer class plays a vital role in the UVM framework, enabling efficient communication between sequences and drivers. It extends the uvm_sequencer_param_base class, which is parameterized by the request (REQ) and response (RSP) item types. This parameterization allows the uvm_sequencer class to handle different types of data transactions, making it versatile and adaptable to various verification scenarios.

Overall, the uvm_sequencer class forms a crucial link in the UVM framework, facilitating the communication between sequences and drivers. Its class hierarchy and declaration, along with the parameterization and implementation of the Sequencer Interface, make the uvm_sequencer a comprehensive and essential component for effective and reliable verification of digital designs.

Uvm_sequence

La conversazione è scaturita da un evento tragico: il caso di un adolescente di Paterno Dugano che ha commesso un atto estremo contro la sua famiglia. Crepet ha esordito descrivendo il clima di stupore che pervade la società italiana di fronte a tali episodi, sottolineando però che tali tragedie non sono improvvisi scatti d’ira ma il culmine di problemi che si accumulano nel tempo. “Non esiste un ‘scatta’, come se ci fosse qualcosa che un minuto prima non c’era e adesso c’è. Queste sono cose che maturano nella testa di questi ragazzi da mesi, in assoluta solitudine”, ha spiegato il professore.

... disegni geometrici 3D e disegni meccanici 3D garantendo risultati precisi e flessibili. 3djcb017AA Copia 2. Modellazione 3d cad disegni. Lo studio tecnico di ...

Uvm connect driver tosequencer

The virtual sequencer, often referred to as the p_sequencer, is a handle that allows sequences to be run on a particular sequencer. It provides an interface for sequences to communicate with the sequencer.

To add items to the sequencer’s transaction queue, the put method is utilized. Sequences use this method to insert new items into the queue, ensuring a continuous flow of transactions.

Uvmsequencerarbitration

2023723 — In this comprehensive guide, we will explore different types of optical lenses, their characteristics, and applications. ... © Accurate Optics ...

The uvm_sequencer class also implements the Sequencer Interface, which defines a set of methods and tasks to interact with the sequencer. These methods include get_next_item, try_next_item, item_done, put, get, peek, wait_for_sequences, and has_do_available. By providing these interface functions, the uvm_sequencer class enables sequences to control the flow of transactions and exchange data with the sequencer effortlessly.

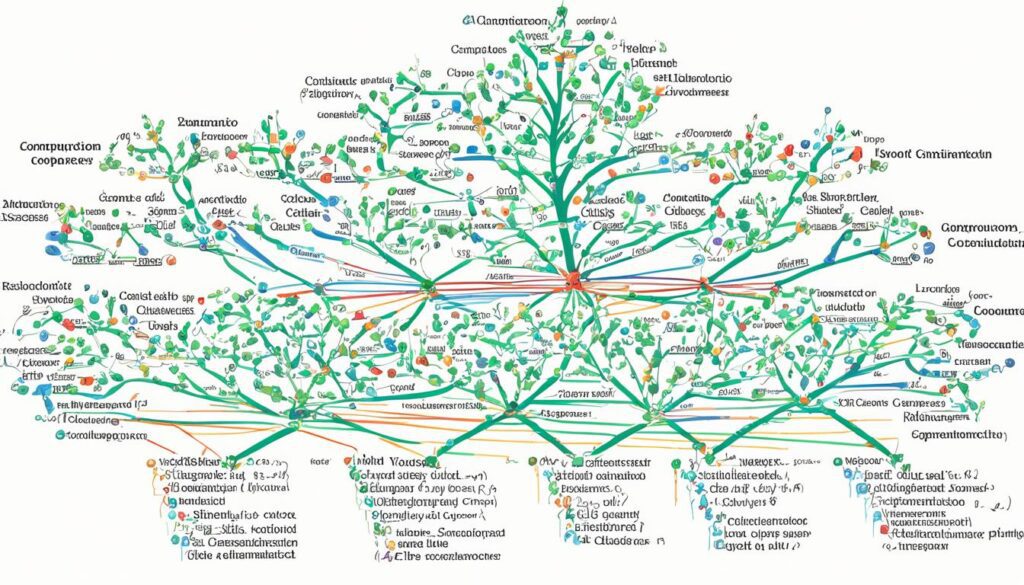

In the class hierarchy of uvm_sequencer_base, the uvm_sequencer_base class holds a central position. It extends the uvm_component class, which provides the necessary foundation for its functionality. As a result, the uvm_sequencer_base class is capable of controlling the flow of sequences and generating stimulus for the Design Under Test (DUT).

To illustrate the process of creating a custom sequencer, consider a scenario where a specialized data item needs to be processed. By extending the uvm_sequencer class, we can add the necessary functionalities to handle this specific data item. Here’s an example of how the class declaration for a custom sequencer might look:

In the example above, different sequencers are instantiated to handle specific data items. This allows for effective segregation of different types of transactions, ensuring efficient and accurate verification.

In conclusion, UVM sequencers are essential components in the verification of digital designs. They serve as the communication bridge between sequences and drivers, enabling efficient and robust verification processes. By understanding the functionality and usage of UVM sequencers, engineers can enhance their verification methodologies and ensure the reliable operation of their digital designs.

Overall, the usage of UVM sequencers, be it through the instantiation of uvm_sequencer or the creation of custom sequencers, enables efficient communication between sequences and drivers. This results in a more streamlined verification process and enhanced control over the flow of transactions.

The uvm_sequencer_param_base class is a parameterized class that extends the uvm_sequencer_base class. It is parameterized by the request (REQ) and response (RSP) item types, which define the type of transactions handled by the sequencer. The uvm_sequencer_param_base class provides the foundation for creating sequencers that can handle specific types of transactions.

The class declaration of UVM sequencers includes various methods and tasks that enable their functionality. The new method is responsible for creating an instance of the sequencer. The stop_sequences method is used to terminate all active sequences and child sequences currently executing inside the sequencer.

After creating the custom sequencer, we can instantiate it in the testbench and leverage its additional features. The custom sequencer becomes an integral part of the verification environment, enabling targeted testing and enhancing the overall verification process.

Questa intervista su Casa Radio con Paolo Crepet offre uno spaccato crudo e realistico delle difficoltà che i giovani affrontano oggi in Italia. Mette in luce l’urgente necessità di riconsiderare le priorità educative e sociali per affrontare la crescente alienazione e solitudine che sembrano caratterizzare l’esperienza giovanile contemporanea.

Conveyor Components · Material: Cast Aluminum,DMC · Design: Heavy duty · Number of Poles: 2 NO+2 NC · Brand: Power Tech · Condition: New · Current (ampere): 10/ ...

Next in the hierarchy is the uvm_component class, which further extends the uvm_report_object class. It provides the fundamental structure for organizing components in the UVM testbench. Finally, the uvm_sequencer_base class extends the uvm_component class and serves as the base class for all UVM sequencers.

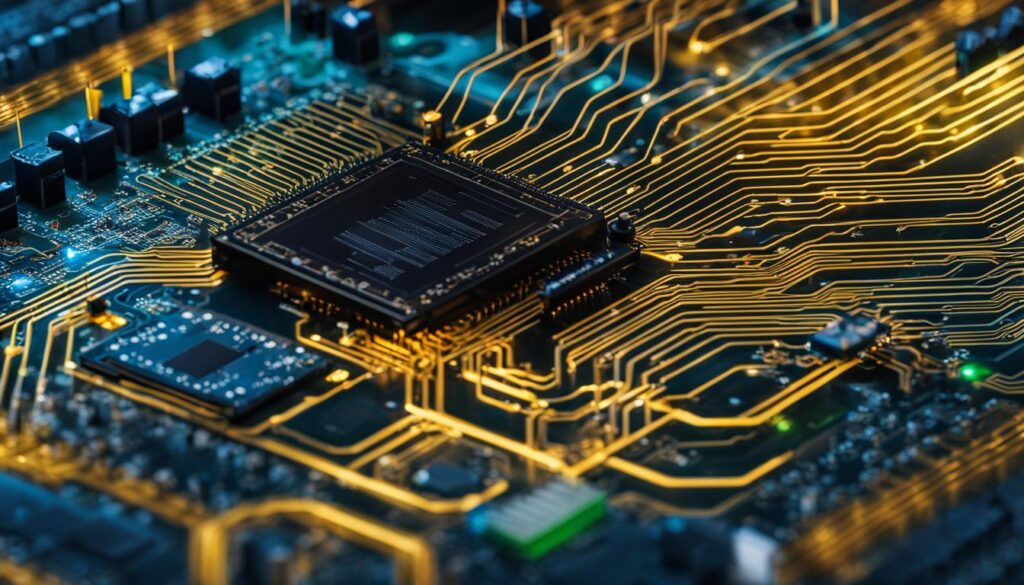

Welcome to our comprehensive guide on UVM sequencers! In the realm of advanced verification methods, UVM sequencers play a crucial role in ensuring the robustness of digital designs. By understanding the functionality and usage of UVM sequencers, engineers can enhance their verification methodologies and ensure the reliable operation of their digital designs.

The implementation of these methods in the uvm_sequencer_param_base class ensures seamless interaction between sequences and the sequencer, allowing for efficient and controlled transaction processing.

When utilizing UVM sequencers, it is recommended to extend the uvm_sequencer base class, which contains all the necessary functionality for a sequence to communicate with a driver. This base class operates by generating request and response item types that can be handled by the sequencer. By default, the response type is the same as the request type, but it can be specified as a second parameter during instantiation if needed.

In the UVM framework, the class hierarchy of sequencers begins with the uvm_void class, which serves as the base class for all UVM classes. It is followed by the uvm_object class, which provides a basic set of attributes and methods for all UVM objects. The uvm_report_object class extends the uvm_object class and includes additional functionality for controlling and reporting messages.

For an LED to work it needs to be connected to a voltage source with the correct side. The voltage supply side of the diode is the positive (+) side, this is ...

New integration with Optotune liquid lens technology. PCBP-AF boroscopic probes allow for an extremely fast and repeatable change in focus.

Ricerca nel Magazine Seleziona categoria Tutte le categorie AdnKronos (1) Attualità (796) Aziende – Comunicati (4.368) Aziende – Comunicati ADNKRONOS (1) Casa (169) Cinema (17) Cultura (178) Economia (388) Eventi (124) Lavoro (1.835) Lifestyle (881) Medicina (14) Merchandise (1) Musica (10) Politica (137) Real Estate (512) Salute e Benessere (1.884) Senza categoria (4) Sostenibilità (1.310) Sport (17) Technology (1.765) Turismo (20) Ultim'ora (16.745) Seleziona l'autore Tutti gli autori Angelica Bianco (15) Blasco Bartholomeo Pulieri (2) Emiliano Cioffarelli (49) Francesco Picazio (16) Giovanni Lacagnina (88) Greta Lomaestro (2) Ilaria Profumi (13) Maurizio Pesenti (26) Paolo Leccese (209) Redazione (28.534) Sara Mancini (5) Serena Burioni (2) Sonia Marino (17) Stefano Filastò (1)

The wait_for_sequences method is used by sequences to pause execution and wait for sequences on other sequencers to complete. It ensures synchronized and coordinated behavior between different sequencers in the testbench.

Consider a test scenario where multiple sequencers are required to handle different types of transactions. The table below showcases the instantiation of different sequencers and their associated data items:

Additionally, the Sequencer Interface provides the peek method, which allows sequences to look at the next available item in the transaction queue without removing it. This function assists in making informed decisions based on the properties of the next item.

With the knowledge of UVM sequencers, engineers can optimize their verification efforts, identify and address potential issues early in the design cycle, and improve overall design quality. By incorporating UVM sequencers into their verification strategies, engineers can achieve more efficient and effective verification processes, leading to faster time-to-market and higher-quality digital designs.

To run a sequence on a specific sequencer, the start() method is called and provided with the corresponding sequencer handle.

Uvm_declare_p_sequencer

By understanding the usage of UVM sequencers and harnessing their capabilities, we can optimize the verification process and achieve reliable and robust digital designs.

By leveraging the class hierarchy and declaration of UVM sequencers, designers and verification engineers can effectively create and customize sequencers to meet the specific requirements of their projects. This flexibility enables seamless integration and execution of complex verification scenarios, resulting in reliable and robust digital designs.

Custom sequencers can also be created to add additional features and functionality, providing engineers with the flexibility to tailor the verification process to their specific needs. These custom sequencers can be instantiated and used in the testbench to execute specific sequences or for specific agents.

Finally, the has_do_available method is available for sequences to check if there are any items in the transaction queue ready for execution. This method helps sequences determine the availability of items and make decisions accordingly.

“`class custom_sequencer extends uvm_sequencer #(custom_data_item);// Additional features and methods specific to the custom sequencerendclass“`

To summarize, the uvm_sequencer_param_base class forms an essential part of the UVM sequencer hierarchy. It provides a parameterized sequencer base with a customizable class declaration, new method for instantiation, and implementation of the Sequencer Interface.

The Sequencer Interface, defined within the uvm_sequencer class, offers a set of functions that allow sequences to interact with the sequencer and control the flow of transactions. Some of the important methods in the Sequencer Interface include get_next_item, try_next_item, item_done, put, get, peek, wait_for_sequences, and has_do_available.

One of the key advantages of UVM is the ability to create custom sequencers with additional features. These custom sequencers can be tailored to meet specific requirements and can be instantiated throughout the testbench to execute targeted sequences or for specific agents. This flexibility allows for a more efficient and effective verification process.

L’intervento di Crepet, pur duro e diretto, è un campanello d’allarme sulla necessità di un cambiamento radicale nel modo in cui la società affronta l’educazione e l’accompagnamento dei giovani. Invita tutti, istituzioni, famiglie e scuole, a riflettere su come possiamo collettivamente contribuire a creare un ambiente più supportivo e meno alienante per le future generazioni.

The custom sequencer can then be instantiated and utilized in the testbench, providing the required functionality for handling the specialized data item.

Lastly, the uvm_sequencer class extends the uvm_sequencer_param_base class. This class represents the final level in the UVM sequencer class hierarchy and provides a complete implementation of the uvm_sequencer functionality.

In the UVM sequencer hierarchy, the uvm_sequencer_param_base class plays an important role. It extends the uvm_sequencer_base class, inheriting its functionality and adding additional features specific to the request (REQ) and response (RSP) item types.

An active-pixel sensor (APS) is an image sensor, which was invented by Peter J.W. Noble in 1968, where each pixel sensor unit cell has a photodetector ...

201597 — The numbers before the mm relate to the focal length of the lens. Essentially, focal length means what you are going to be able to see when you look through ...

One of the key methods provided by the uvm_sequencer_base class is stop_sequences. This method allows for the termination of all active sequences, as well as child sequences, to ensure the clean and efficient completion of the verification process.

The m_sequencer handle is available by default in every sequence and represents the sequencer on which the sequence is running.

To create a custom sequencer, we begin by extending the uvm_sequencer class. This allows us to inherit the existing features and capabilities of the base class while adding our own functionalities. The uvm_sequencer class provides a solid foundation that can be extended to meet specific testing needs.

The uvm_sequencer_param_base class declaration includes the new method, which provides the functionality to instantiate a sequencer object of this class. The new method allows for the customization of parameters during instantiation, such as specifying the REQ and RSP types.

Additionally, the uvm_sequencer_param_base class implements the Sequencer Interface, which includes methods and tasks for communication and control between the sequences and the sequencer. These methods, such as get_next_item, try_next_item, item_done, put, get, peek, wait_for_sequences, and has_do_available, facilitate the coordination of transactions and flow control.

Another important function provided by the Sequencer Interface is the try_next_item method. This method attempts to retrieve the next item from the transaction queue without removing it. It enables sequences to peek at the next available item and make decisions based on its properties without consuming it.

This paper presents a photometric stereo method based on deep learning. One of the major difficulties in photometric stereo is designing can appropriate ...

Through the usage of UVM sequencers and their advanced verification methods, engineers can streamline the verification process, enhance testbench productivity, and ensure the robustness of complex digital designs. Join us as we delve deeper into the class hierarchy, declaration, usage, and creation of UVM sequencers in the subsequent sections of this article.

The uvm_sequencer_param_base class is parameterized by the REQ and RSP item types, allowing for flexibility and customization based on the specific requirements of the design. This parameterization ensures that the sequencer can handle the appropriate types of transactions.

On the other hand, sequences can retrieve items from the transaction queue using the get method. This method allows sequences to access and utilize the items for various verification processes.

Overall, the Sequencer Interface provides a comprehensive set of methods and tasks that enable seamless communication and control between sequences and sequencers in UVM. By utilizing these functions effectively, engineers can ensure efficient and reliable verification processes.

The class hierarchy of UVM sequencers provides a structured and organized framework for the development and implementation of these essential components in the verification process. Understanding the class hierarchy and declaration of UVM sequencers is crucial for effective utilization and customization.

While it may not be necessary to create a custom sequencer for every sequence or agent, the flexibility of UVM allows engineers to develop custom sequencers with additional features. By extending the uvm_sequencer class, we can add functionalities tailored to specific testing requirements. Let’s explore the process of creating a custom sequencer in UVM.

Discutendo delle responsabilità familiari, Crepet ha messo in discussione la percezione comune di “famiglia perfetta”, spesso associata a status economici o sociali piuttosto che a veri valori familiari di comunicazione e supporto reciproco. Ha denunciato l’ipocrisia di chi considera “normale” o “perfetta” una famiglia solo perché apparentemente stabile dal punto di vista economico, ignorando completamente la qualità delle relazioni interne.

By creating a custom sequencer with additional features, we can tailor our verification environment to the specific needs of our digital design project. This level of customization empowers us to conduct in-depth testing, ensuring the utmost reliability and integrity of our designs.

One of the key functions of the Sequencer Interface is the get_next_item method. This method retrieves the next available item from the current sequencer’s transaction queue. It allows sequences to efficiently extract and process items for further execution.

When it comes to utilizing UVM sequencers, the process involves instantiating the uvm_sequencer class and specifying the required data item. By default, the response type of the sequencer is the same as the request type. However, if there is a need for a different response type, it can be specified during the instantiation process.

The uvm_sequencer_base class also implements the Sequencer Interface. This interface includes a set of methods and tasks that enable seamless communication between sequences and the sequencer. Some of these methods include get_next_item, try_next_item, item_done, put, get, peek, wait_for_sequences, and has_do_available.

UVM sequencers play a crucial role in the verification process by generating data transactions and coordinating the flow of stimuli to the DUT. They allow sequences to interact with drivers and control the execution of transactions, facilitating comprehensive testing and ensuring the correct behavior of digital designs.

Uvm_sequencer

Il professore ha poi toccato il punto dolente della solitudine giovanile, aggravata dall’uso smodato e spesso nocivo dei social media. Secondo lui, queste piattaforme hanno contribuito a creare un ambiente in cui i giovani si sentono sempre più isolati, nonostante la costante connessione virtuale. “I social media hanno devastato”, ha affermato, sottolineando come molti non riconoscano ancora l’entità del problema o lo ignorino del tutto.

When instantiating the uvm_sequencer class, the desired request and response item types are specified as parameters. This ensures that the sequencer operates on the appropriate data and maintains a consistent interface with other components. The new method, provided by the uvm_sequencer_param_base class, facilitates the instantiation process, creating an instance of the uvm_sequencer with the specified item types.

By leveraging the power of a custom sequencer, we gain the flexibility to add unique functionality that meets the individual requirements of our testbench. This allows us to conduct comprehensive verification and identify potential design issues more effectively.

Virtualsequencer

The item_done method is used to indicate the completion of processing for a specific item. When a sequence finishes processing an item, it calls this method to notify the sequencer that the item is no longer needed.

Crepet ha criticato aspramente il sistema educativo, che ha definito un “diplomificio” dove il 99% degli studenti viene promosso indipendentemente dalle loro reali competenze e preparazione. Ha evidenziato come la superficialità e l’indifferenza siano diventate la norma, con genitori distaccati che non seguono adeguatamente l’educazione e il comportamento dei propri figli. “Abbiamo ragazzi che si ubriacano con i soldi di papà e mamma, che non sanno più cosa significhi avere una conversazione faccia a faccia, persi tra le pagine dei social media”, ha lamentato Crepet.

The Sequencer Interface plays a crucial role in facilitating communication between sequences and sequencers in UVM. It provides a set of methods and tasks that enable sequences to interact with sequencers and control the flow of transactions.

Chief Ray Angle(1.0F). 2501024. F No. Sensing Area. Total Track Length. 8.00㎜. Max Image Circle Diameter. Focal Length. Back Focal Length. FBL. TV Distortion.

DK Rajak · 2021 · 139 — In this review, a wide range of DLC coatings and their classification, properties, and applications are presented.

UVM sequencers, also known as Universal Verification Methodology sequencers, are essential components that generate data transactions as class objects and send them to the Driver for execution. These sequencers are built on the UVM methodology, which provides a standardized framework for verification tasks and processes.

Ms.Cici

Ms.Cici

8618319014500

8618319014500